UART

.

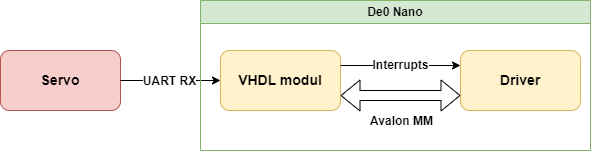

Every motor is equipped with its own UART RX connection to the FPGA system, and each connection is managed by a distinct UART module. These UART modules are individually accessible via their corresponding Linux device drivers, ensuring dedicated communication channels for each motor.

Upon initialization, the driver configures the UART module and enters a standby mode, awaiting interrupts. The driver is programmed to handle two distinct types of interrupts, ensuring robust data management and communication integrity.

Firstly, an interrupt is triggered for every transmitted data byte. When such an interrupt occurs, the driver reads the data byte and stores it in an internal buffer. This process continues for each subsequent data byte, maintaining a sequential and organized data flow.

Secondly, a timeout interrupt signals the system that the data transmission is complete. This interrupt serves as an indicator that no more data bytes are expected. Upon receiving this interrupt, the driver validates the integrity of the transmitted data. Following validation, the driver transfers the data from the internal buffer to another buffer, which is designed to be accessible from userspace.